کتاب مدار منطقی (طراحی دیجیتال ) موریس مانو

تایپ شده با کیفیت بالا و قابلیت جستجو

ویرایش 5

فرمت :PDF

دانلود کتاب

خلاصه ای از فصل های کتاب:

در زیر خلاصه ای از موضوعاتی است که در هر فصل به آن پرداخته شده است.

فصل 1 سیستم های مختلف دودویی مناسب برای نمایش اطلاعات در سیستم های دیجیتال را ارائه می دهد. سیستم اعداد دودویی توضیح داده شده و کدهای دودویی نشان داده شده است. مثالهایی برای جمع و تفریق اعداد دودویی علامتدار و اعداد اعشاری در قالب اعشاری با کد دودویی (BCD) ارائه شدهاند.

فصل 2 مقدمات اساسی جبر بولی را معرفی می کند و همبستگی بین عبارات بولی و نمودارهای منطقی مربوط به آن ها را نشان می دهد. تمام عملیات منطقی ممکن برای دو متغیر بررسی شده و مفیدترین گیت های منطقی مورد استفاده در طراحی سیستم های دیجیتال شناسایی می شوند. این فصل هم چنین گیت های منطقی CMOS را معرفی می کند.

دانلود کتاب طراحی دیجیتال موریس مانو ویرایش پنجم

فصل 3 روش نقشه برای ساده سازی عبارات بولی را پوشش می دهد. روش نقشه هم چنین برای ساده سازی مدارهای دیجیتالی ساخته شده با گیت های AND-OR، NAND یا NOR استفاده می شود. تمام مدارهای گیت دو سطحی ممکن دیگر در نظر گرفته شده و روش اجرای آن ها توضیح داده شده است. Verilog HDL همراه با نمونه های ساده از مدل های سطح گیت معرفی شده است.

فصل 4 روش های رسمی برای تجزیه و تحلیل و طراحی مدارهای ترکیبی را تشریح می کند. برخی از اجزای اساسی مورد استفاده در طراحی سیستم های دیجیتال مانند جمع کننده ها و مبدل های کد به عنوان نمونه طراحی معرفی شده اند. توابع منطقی دیجیتال پرکاربرد مانند جمع کننده ها و تفریق کننده های موازی، دیکدرها، انکدرها و مالتی پلکسرها توضیح داده شده و کاربرد آن ها در طراحی مدارهای ترکیبی نشان داده شده است. مثالهای HDL در مدلهای سطح گیت، جریان داده و رفتاری ارائه میشوند تا راههای جایگزین موجود برای توصیف مدارهای ترکیبی در Verilog HDL را نشان دهند. روش نوشتن یک برنامه آزمون ساده برای ارائه محرک به طراحی HDL ارائه شده است.

فصل 5 روش های رسمی برای تجزیه و تحلیل و طراحی مدارهای ترتیبی کلاک (همزمان) را تشریح می کند. ساختار گیت چندین نوع فلیپ فلاپ همراه با بحثی در مورد تفاوت بین سطح و راه اندازی لبه ارائه شده است. مثال های خاصی برای نشان دادن مشتق جدول حالت و نمودار حالت در هنگام تجزیه و تحلیل مدار ترتیبی استفاده می شود. تعدادی از نمونههای طراحی با تأکید بر مدارهای متوالی که از فلیپ فلاپهای نوع D استفاده میکنند، ارائه شدهاند. مدل سازی رفتاری در Verilog HDL برای مدارهای ترتیبی توضیح داده شده است. مثالهای HDL برای نشان دادن مدلهای Mealy و Moore مدارهای ترتیبی ارائه شدهاند.

فصل 6 به اجزای مختلف مدار متوالی مانند رجیسترها، شیفت رجیسترها و شمارنده می پردازد. این اجزای دیجیتالی بلوک های ساختمانی اساسی هستند که از آن ها سیستم های دیجیتال پیچیده تر ساخته می شوند. توضیحات HDL از شیفت رجیسترها و شمارنده ارائه شده است.

دانلود کتاب طراحی دیجیتال موریس مانو ترجمه فارسی

فصل 7 به حافظه دسترسی تصادفی (RAM) و دستگاه های منطقی قابل برنامه ریزی می پردازد. رمزگشایی حافظه و طرح های تصحیح خطا مورد بحث قرار می گیرد. دستگاه های قابل برنامه ریزی ترکیبی و ترتیبی مانند ROM ها، PLA ها، PAL ها، CPLD ها و FPGA ها ارائه شده اند.

فصل 8 به نمایش سطح انتقال رجیستر (RTL) سیستم های دیجیتال می پردازد. نمودار ماشین حالت الگوریتمی (ASM) معرفی شده است. تعدادی از مثال ها استفاده از نمودار ASM، نمودار ASMD، نمایش RTL و توضیحات HDL را در طراحی سیستم های دیجیتال نشان می دهد. طراحی یک ماشین حالت محدود برای کنترل یک مسیر داده با جزئیات ارائه شده است، از جمله موقعیت واقعی که در آن سیگنالهای وضعیت از مسیر داده توسط ماشین حالتی که آن را کنترل میکند استفاده میشود. این فصل مهم ترین فصل کتاب است زیرا رویکردی سیستماتیک به پروژه های طراحی پیشرفته تر را در اختیار دانشجو قرار می دهد.

فصل 9 به تشریح آزمایشهایی میپردازد که میتوان در آزمایشگاه با سختافزاری که بهراحتی در دسترس تجاری است، انجام داد. عملکرد آی سی های مورد استفاده در آزمایش ها با مراجعه به نمودارهای اجزای مشابه معرفی شده در فصل های قبل توضیح داده شده است. هر آزمایش به صورت غیر رسمی ارائه می شود و از دانشجو انتظار می رود مدار را طراحی کرده و روشی برای بررسی عملکرد آن در آزمایشگاه فرموله کند. آزمایشهای آزمایشگاهی را میتوان به صورت مستقل نیز مورد استفاده قرار داد و میتواند با رویکرد سنتی، با نمونه تابلو و مدارهای TTL، یا با رویکرد HDL/سنتز با استفاده از FPGA انجام شود. امروزه نرمافزاری برای سنتز یک مدل HDL و پیادهسازی مدار با یک FPGA بدون هیچ هزینهای از فروشندگان FPGA در دسترس است و به دانشجویان این امکان را میدهد تا قبل از استفاده از تابلوهای نمونهسازی و سایر منابع در آزمایشگاه، مقدار قابل توجهی کار را در محیط شخصی خود انجام دهند. بردهای مدار برای نمونه سازی سریع مدارها با FPGA با هزینه اسمی در دسترس هستند و معمولاً شامل دکمه های فشاری، سوئیچ ها، نمایشگرهای هفت بخش، LCD، صفحه کلید و سایر دستگاه های ورودی/خروجی هستند. با استفاده از این منابع، دانشجویان میتوانند تمرینهای آزمایشگاهی تجویز شده یا پروژههای خود را انجام دهند و فوراً نتیجه بگیرند.

فصل 10 نمادهای گرافیکی استاندارد را برای توابع منطقی که توسط یک استاندارد ANSI/IEEE توصیه شده است، ارائه می کند. این نمادهای گرافیکی برای اجزای یکپارچه سازی در مقیاس کوچک (SSI) و یکپارچه سازی مقیاس متوسط (MSI) توسعه داده شده اند تا کاربر بتواند هر تابع را از نماد گرافیکی منحصر به فرد اختصاص داده شده تشخیص دهد. این فصل نمادهای گرافیکی استاندارد IC های مورد استفاده در آزمایشات آزمایشگاهی را نشان می دهد.

دانلود ترجمه کتاب طراحی دیجیتال موریس مانو

بخشی از متن کتاب:

هنگامی که یک عبارت بولی با گیتهای منطقی پیاده سازی میشود، هر عبارت به یک گیت نیاز دارد و هر متغیر درون عبارت یک ورودی گیت را مشخص میکند. ما یک متغیر را به عنوان یک متغیر واحد در یک عبارت، به صورت مکمل یا غیر مکمل تعریف میکنیم. تابع شکل 2.2 (الف) دارای سه عبارت و هشت متغیر است و تابع شکل 2.2 (ب) دارای دو عبارت و چهار متغیر است. با کاهش تعداد عبارتها، تعداد متغیرها یا هر دو در یک عبارت بولی، اغلب میتوان مدار سادهتری به دست آورد. اعمال جبر بولی بیشتر شامل کاهش یک عبارت به منظور به دست آوردن یک مدار سادهتر است. توابع حداکثر پنج متغیری را میتوان با روش نقشه توضیح داده شده در فصل بعدی ساده کرد. برای توابع پیچیده بولی و بسیاری از خروجی های مختلف، طراحان مدارهای دیجیتال از برنامه های کمینه سازی کامپیوتری استفاده میکنند که قادر به تولید مدارهای بهینه با میلیونnها گیت منطقی هستند. مفاهیم معرفی شده در این فصل چارچوبی را برای آن ابزارها فراهم میکند. تنها روش دستی موجود، یک روش برش و آزمایش است که از روابط اولیه و سایر تکنیکهای عملیات استفاده میکند که هنگام استفاده شناخته میشوند، اما با این وجود، مشمول خطای انسانی هستند. مثالهایی که در ادامه میآیند، عملیات جبری جبر بولی را برای آشنا کردن خواننده با این کار مهم طراحی نشان میدهند.

به حداقل رساندن سطح گیت، وظیفه طراحی یافتن پیادهسازی بهینه در سطح گیت از توابع بولی است که یک مدار دیجیتال را توصیف میکند. این کار به خوبی درک شده است، اما زمانی که منطق بیش از چند ورودی دارد، پیادهسازی آن با روشهای دستی دشوار است. خوشبختانه، ابزارهای سنتز منطق مبتنی بر کامپیوتر میتوانند مجموعه بزرگی از معادلات بولی را به طور موثر و سریع به حداقل برسانند. با این وجود، این مهم است که یک طراح توضیحات ریاضی و حل مسئله را درک کند. این فصل به عنوان پایهای برای درک شما از آن موضوع مهم عمل میکند و شما را قادر میسازد تا یک طراحی دستی مدارهای ساده را اجرا کنید و شما را برای استفاده ماهرانه از ابزارهای طراحی مدرن آماده میکند. این فصل همچنین یک زبان توصیف سخت افزار را معرفی میکند که توسط ابزارهای طراحی مدرن استفاده میشود.

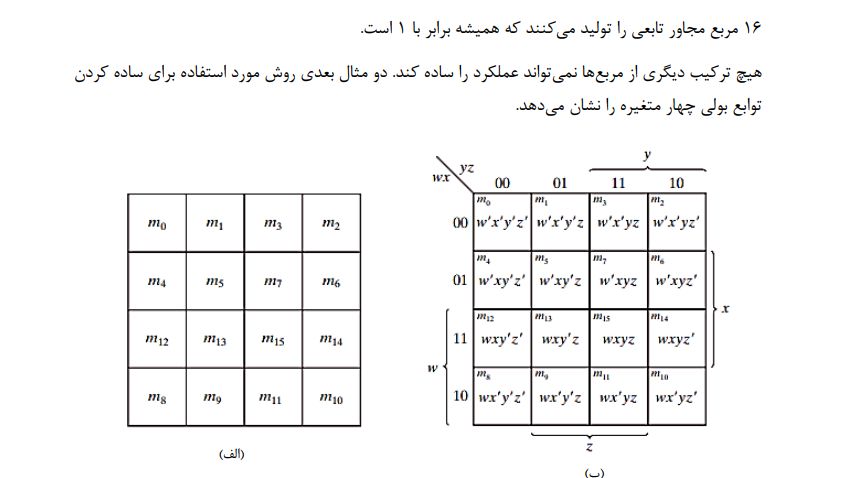

پیچیدگی گیتهای منطقی دیجیتالی که یک تابع بولی را پیادهسازی میکنند، مستقیماً با پیچیدگی عبارت جبری که تابع از آن پیادهسازی میشود، مرتبط است. اگرچه نمایش جدول درستی یک تابع منحصربهفرد است، اما وقتی به صورت جبری بیان میشود، میتواند به اشکال مختلف، اما معادل، ظاهر شود. عبارات بولی ممکن است با ابزار جبری ساده شود همانطور که در بخش 4.2 بحث شد. با این حال، این روش به حداقل رساندن ناخوشایند است زیرا فاقد قوانین خاصی برای پیشبینی هر مرحله بعدی در فرآیند دستکاری است. روش نقشه ارائه شده در اینجا یک روش ساده و ساده برای به حداقل رساندن توابع بولی ارائه می دهد. این روش ممکن است به عنوان شکل تصویری یک جدول درستی در نظر گرفته شود. روش جدول به نقشه کارنو یا نقشه K نیز معروف است.

انتهای رپرتاژ آگهی/